# Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica

# Actividad Fundamental 1 (AF1) Electrónica Digital 1

|  | Hora               | NL | Matricula | Nombre           |                  | Equipo |

|--|--------------------|----|-----------|------------------|------------------|--------|

|  | M2 11 2045253 Gard |    | 2045253   | García Gaytán    | Christian Axel   | 4      |

|  | IVIZ               | 20 | 1965452   | Martínez Cázares | Gerardo de Jesús | 4      |

En esta actividad fundamental se adquieren los conocimientos y desarrollan las habilidades en el manejo de herramientas de diseño de sistemas digitales, que se evaluarán en el próximo examen de medio curso, por lo que es indispensable entregarla en tiempo y forma.

En esta actividad se solicita:

- 1.- Diseñar, efectuar la simulación y construir el prototipo del sistema digital propuesto, así como documentar el proceso de diseño.

- 2.- Cada uno de los integrantes del equipo debe de subir los archivos entregables solicitados a la plataforma Google Classroom antes de la fecha límite señalada.

- 3.- Una vez cumplido con lo anterior, el equipo debe de solicitar una entrevista presencial con los becarios, para mostrar los prototipos, así como explicar el procedimiento y resultados obtenidos, esto antes de la fecha límite acordada.

### Sistema Digital propuesto

El problema de diseño combinacional planteado se refiere a una empresa con cinco accionistas (A, B, C, D y E), cuyas acciones están distribuidas de la siguiente manera:

A=35%, B=35%, C=10%, D=10% y E=10%.

Se requiere diseñar, simular y construir un sistema digital para el escrutinio en la toma de decisiones. La opinión se obtiene a través de botones de votación, uno para cada accionista (A, B, C, D y E respectivamente). Es importante tener en cuenta que cada accionista tiene un porcentaje ponderado en su voto, igual al número de acciones que posee.

El resultado de la votación será mostrado por medio de dos leds (**L1 y L0**) de salida de la siguiente manera:

| L1 | L0 |                                        |  |

|----|----|----------------------------------------|--|

| 0  | 0  | No Hay resultado o menor o igual a 30% |  |

| 0  | 1  | Mayor que 30% 0 Menor o igual a 50%    |  |

| 1  | 0  | Mayor que 50% y menor o igual a 70%    |  |

| 1  | 1  | Mayor de 70%                           |  |

Los valores de las salidas L1 y L0 se mostrarán en forma visual por medio de Leds en donde el valor de 0 el Led deberá de estar apagado y en el valor de 1 el led deberá de encender.

El diseño del sistema debe tomar en cuenta estas especificaciones y cumplir con los requerimientos mencionados. Se realizará una simulación para verificar su correcto funcionamiento y, posteriormente, se construirá un prototipo físico utilizando componentes electrónicos adecuados.

La fecha límite para subir los archivos es el martes 27 de febrero y para la entrevista miércoles 28 del mismo mes.

|                                  | Enero - Febrero 2024 |    |                      |    |    |    |

|----------------------------------|----------------------|----|----------------------|----|----|----|

| L                                | М                    | М  | J                    | ٧  | S  | D  |

| 29                               | 30                   | 31 | 1                    | 2  | 3  | 4  |

| 5                                | 6                    | 7  | 8                    | 9  | 10 | 11 |

| 12                               | 13                   | 14 | 15                   | 16 | 17 | 18 |

| 19                               | 20                   | 21 | 22                   | 23 | 24 | 25 |

| 26                               | 27                   | 28 |                      |    |    |    |

| Se previsor, evita contratiempos |                      |    |                      |    |    |    |

| 27 fecha limite GC               |                      |    | echa lín<br>ntrevist |    |    |    |

Dr. Arnulfo Treviño Cubero Director de la F.I.M.E

No basta saber, se debe también aplicar. No es suficiente querer, se debe también hacer.

Johann Wolfgang Goethe (1749-1832) Poeta y dramaturgo alemán.

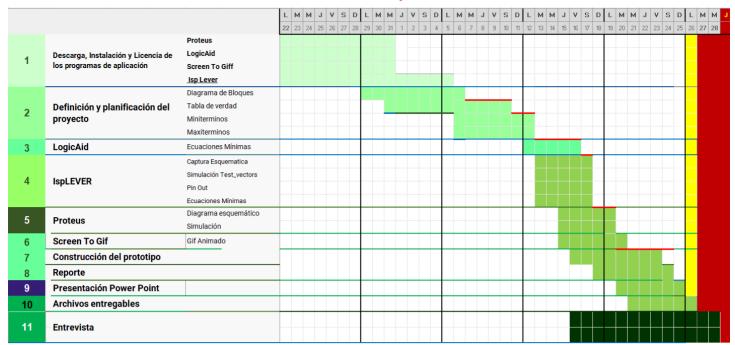

# **Cronograma Propuesto**

# Descripción de las Fases

| 1  | Descarga, Instalación y Licencia de los programas de aplicación <b>ispLEVER, PROTEUS, LogicAid y ScreenToGif</b> :                                                                                          |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|    | Lectura comprensiva del problema, identificación de variables de Entrada y Salida, Diagrama de Bloques                                                                                                      |  |  |

| 2  | Planteamiento, trasladar el comportamiento a una Tabla de Verdad                                                                                                                                            |  |  |

|    | Obtener las ecuaciones de <b>Minitérminos</b> y/o <b>Maxitérminos</b> en <b>SOP</b> y/o <b>POS</b> según convenga y representarlas también en sus formas canónicas $\sum$ y $\Pi$ .                         |  |  |

| 3  | Obtener las Ecuaciones mínimas por medio del programa LogicAid (ecuaciones, términos o tabla de verdad), indicando la cantidad de entradas (Input Cost) y la cantidad de compuertas utilizadas (Gate Cost). |  |  |

| 4  | Realizar la Captura esquemática Diagrama esquemático compuertas lógicas AON utilizando Schematic del programa IspLEVER (ecuaciones mínimas) de la opción más conveniente SOP o POS.                         |  |  |

| Ľ  | Generar el Archivo <b>ABV</b> y obtener la <b>Simulación</b> Test_vectors (IspLEVER).                                                                                                                       |  |  |

| 5  | Elaborar el Diagrama lógico en PROTEUS con el Dispositivo AM22V10, usando como entradas interruptores, resistencias y LEDS y como salidas que se muestren a través de Leds.                                 |  |  |

| 6  | Generar animación o video de la simulación del funcionamiento de todas las combinaciones posibles (ScreenToGif)                                                                                             |  |  |

| 7  | Construir el prototipo                                                                                                                                                                                      |  |  |

| 8  | Realizar el Reporte con lo solicitado (ver detalle en la página siguiente).                                                                                                                                 |  |  |

| 9  | Realizarla presentación en Power Point con las diapositivas solicitadas                                                                                                                                     |  |  |

| 10 | Subir a Google Classroom los archivos entregables solicitados comprimidos en una carpeta en formato ZIP o RAR.                                                                                              |  |  |

| 11 | Agendar una entrevista presencial para la presentación del Proyecto todo el equipo (Power Point, ISP, Proteus)                                                                                              |  |  |

|    |                                                                                                                                                                                                             |  |  |

### Reporte (Pdf)

#### 1.- Portada

- a). U.A.N.L. F.I.M.E. (logotipos y nombres) y Nombre del curso

- b). Número y nombre de la actividad

- c). Nombre, número de matrícula del Alumno y Programa Educativo

- d). Hora del grupo y número de lista

- e). Fecha de elaboración.

- f). Tiempo estimado que se le dedico a esta actividad (horas)

- 2.- Redacción del problema.

- 3.- Diagrama de Bloques (Definición de las Entradas y salidas).

- 4.- Tabla de Verdad.

- 5.- Ecuaciones de los minitérminos y/o maxitérminos según convenga (SOP o POS).

- 6.- Ecuaciones mínimas SOP y POS indicando la cantidad de entradas y compuertas

- 7.- Diagrama esquemático (figura del archivo SCH).

- 8.-Código de la simulación ABV (código del archivo).

- 9.- Imagen de la Simulación Test\_vectors (captura de pantalla).

- 10.- Diagrama de la distribución de terminales (pin out) mostradas en el del archivo RPT.

- 11.- Imagen del circuito en PROTEUS (usando Logic State como entradas y Logic Probe como salidas).

- 12.- Las Ecuaciones mínimas mostradas en el archivo RPT.

- 13 Archivo JED

- 14.- Foto del prototipo implementado.

- 15.- Bibliografía completa.

- 16.- Conclusiones, cada miembro del equipo debe de redactar su propia conclusión.

### Un reporte sin conclusiones carece de valor.

17.- Recomendaciones.

### Presentación en Power Point (diapositivas recomendadas para la presentación en la entrevista)

- 1.- Portada.

- 2.- Redacción del problema.

- 3.- Diagrama de Bloques y Tabla de Verdad.

- 4.- Ecuaciones de Minitérminos (SOP) y/o Maxitérminos (POS).

- 5.- Ecuaciones mínimas SOP y POS (LogicAid)

- 6.- Imagen del Diagrama esquemático de compuertas en la forma AON.

- 7.- Imágenes: archivo con código ABV, imagen de la distribución de terminales (pin out).

- 8.- Imagen de la simulación de Test\_Vectors.

- 9.- Diagrama lógico en Proteus y Gif animado.

- 10.- Foto del prototipo implementado

- 11.- Conclusiones de cada integrante

- 12.- Recomendaciones.

Antes de agendar la cita para mostrar el prototipo, explicar el procedimiento y resultados obtenidos, cada integrante debe de subir a Google Classroom los archivos entregables listados abajo:

|   | Archivos Entregables               | extensión |                                                                                |

|---|------------------------------------|-----------|--------------------------------------------------------------------------------|

| 1 | Reporte completo                   | PDF       | Tadaa inahiidaa ay uu aala ayahiya ZID a DAD                                   |

| 2 | Archivo de Captura<br>Esquemática  | SCH       | Todos incluidos en un solo archivo ZIP o RAR<br>llamado                        |

| 3 | Archivos de las Ecuaciones mínimas | AID y OUT | AF1MXNLY. <b>AF1</b> =Actividad Fundamental 1 <b>X</b> =hora, <b>Y</b> =No. de |

| 4 | PROTEUS                            | PSDPRJ    | lista                                                                          |

| 5 | Archivo JEDEC                      | JED       | Ejemplo                                                                        |

| 6 | Archivo de Simulación ABEL         | ABV       | AF1M1NL03:zip                                                                  |

| 7 | Animación de la simulación         | GIF       |                                                                                |

| 8 | Presentación                       | PPT       |                                                                                |

### Importante:

Con el profesor o los becarios podrás solicitar asesorías/revisión de actividades y proyectos, de forma presencial.

# Material necesario para el desarrollo de las prácticas y proyectos de Electrónica Digital I Paquete de inicio

| Cant. | descripción                                                            |  |

|-------|------------------------------------------------------------------------|--|

| 30    | Resistores de 330 $\Omega$ a 1/4 W                                     |  |

| 15    | Led's de 5 mm económico diferentes colores, ámbar, rojos y verdes.     |  |

| 1     | Display de 7 segmentos (Cátodo o Ánodo Común)                          |  |

| 1     | Tablilla de conexiones (Proto-Board) 1 Bloque 2 Tiras 830 puntos       |  |

| 1     | DIP Switch deslizable (8 interruptores deslizables) tipo TTL           |  |

| 1     | Metro de cable para alambrar calibre 22                                |  |

| 6     | Switch Push Micro NO (interruptor de no retención normalmente abierto) |  |

| 1     | Dispositivo Logico Programable ATF22V10 Microchip o equivalente.       |  |

# Paquete pulso

| Cant. | descripción                                |         |  |

|-------|--------------------------------------------|---------|--|

| 1     | Potenciómetro Miniatura (270º)             | 5 kΩ    |  |

| 1     | Capacitor electrolítico 25V                | 470 μF  |  |

| 1     | Capacitor electrolítico 25V                | 1000 μF |  |

| 1     | Compuerta Nand de 2 entradas o equivalente | SN7400  |  |

| 1     | Compuerta Not con Schmitt Trigger          | SN7414  |  |

# **Material opcional**

| Cant. | descripción                                        |         |  |

|-------|----------------------------------------------------|---------|--|

| 1     | Terminal Block                                     |         |  |

| 1     | Matriz de transistores Darlington de 50 V y 500 mA | ULN2803 |  |

| 1     | Juego de cables Jumpers para Protoboard            |         |  |

# Sugerencias de proveedores

| Proveedor                       | Dirección                                        | Contacto               |  |

|---------------------------------|--------------------------------------------------|------------------------|--|

| AG Electrónica                  | Colón 171 Poniente, Mty.                         | www.agelectronica.com/ |  |

| Electrónica 175                 | Colon 205 Ote.                                   | www.e175.mx            |  |

| Electrónica para<br>Estudiantes | Colon 173 Pte.                                   | www.semty.mx           |  |

| IRD                             | Edificio 7 primer piso FIME                      |                        |  |

| Mecatronium                     | Máquina expendedora edificio 7 segundo piso FIME | chips.mecatronium.com/ |  |

| Zenerbyte                       | Entrega en FIME                                  | 8113984239             |  |

# Beneficios del Trabajo en equipo

Es una actividad que favorece el aprendizaje integral de los estudiantes.

Saber trabajar en equipo es una aptitud fundamental necesaria a lo largo de nuestra vida, en especial a nivel laboral como ingeniero.

Aprenderás a trabajar en consonancia con tus compañeros, de manera que será más fácil terminar las actividades dentro del plazo establecido.

En el caso de que surjan problemas, en el equipo se pueden proponer soluciones al respecto trabajando individualmente serían más difíciles de encontrar.

Trabajar junto con otras personas mientras se persigue el mismo objetivo, fomenta entre otras cosas la comunicación, el respeto mutuo, el sentido de la identidad y la solidaridad.

Mejora la comunicación y el diálogo: a la hora de trabajar en equipo surgen situaciones donde las distintas partes no están de acuerdo o expresan diferentes puntos de vista. Aprender a debatir en estos momentos es fundamental para no generar discusiones.

Todo equipo necesita definir sus normas de convivencias, por ejemplo:

### 1.- Horarios de trabajo

Es necesario empatar agendas, para establecer reuniones periódicas presenciales o en línea, se recomienda por lo menos dos reuniones por semana de una hora de duración.

Iniciando con la lectura comprensiva del problema, en donde se identifican las variables Entrada y Salida, y se elabora el Diagrama de Bloques

### 2.- Formas de comunicación

La comunicación y el seguimiento son herramientas fundamentales para realizar el trabajo en equipo.

# 3.- Recursos

Revisar si se cuenta con los elementos suficientes para elaborar el proyecto solicitado.

### **Nota Importante:**

En el caso de que uno o varios de los miembros del equipo, tenga problemas para participar, favor de comunicarlo lo más pronto posible al profesor o becarios para tomar las medidas pertinentes.

"La fuerza del equipo viene de cada miembro. La fuerza de cada miembro es el equipo."

Phil Jackson