## Universidad Autónoma de Nuevo León Facultad de Ingeniería Mecánica y Eléctrica

### Coordinación General de Ingeniería Electrónica

P1 - 2024

#### Laboratorio de Electrónica Digital I Sesión 6

| Hora | PE  | NL | Mat     | Apellidos  | Nombre         |

|------|-----|----|---------|------------|----------------|

| MM1  | IMC | 13 | 1926053 | Lujan Arce | Adrián Eduardo |

#### Diseño de sistemas combinacionales

Propósito: Comprensión, análisis y aplicación del método de Diseño de sistemas combinacionales, mediante el diseño, la simulación y construcción de un prototipo

Método del diseño combinacional con HDL

- 1.- Especificar el sistema.

- 2.-Determinar entradas y salidas (Diagrama de Bloques).

| 3 Trasladar el comportamiento a una tabla de verdad.                     | Código   |  |  |  |

|--------------------------------------------------------------------------|----------|--|--|--|

| Representar la ecuación en sus formas canónicas SOP $\Sigma$ y POS $\Pi$ |          |  |  |  |

| 4 Ecuaciones Mínimas                                                     | ABEL-HDL |  |  |  |

- 5.-Simulación.

- 6.- Construcción del prototipo

- 1.- Especificar el sistema Problema propuesto:

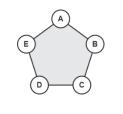

Diseñe y efectué la simulación de un sistema digital binario, para el control de alerta de un sistema de producción que es alimentado por 5 generadores llamados A, B, C, D y E, distribuidos como lo muestra la figura.

Si el generador trabaja correctamente el sistema lo indica por medio de una señal baja (0) y en caso de falla una señal alta (1).

Para asegurar el buen funcionamiento del sistema se requieren dos salidas que corresponden a dos tipos de señales de alerta con las siguientes condiciones:

- 1.- Alarma luminosa (AL) que se activa AL=1, sí solo dos generadores contiguos fallan o solo tres generadores contiguos fallan, incluyendo el caso en donde todos los generadores fallan.

- 2.- Alarma acústica (AA) que toma el valor de AA=1, cuando al menos tres generadores fallan y éstos sean todos contiguos, excluyendo el caso en donde todos los generadores fallan

| <b> Determinar entradas y salidas</b> (Dibujo del Diagrama de Bloques). |  |  |  |  |  |  |

|-------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                         |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |

|                                                                         |  |  |  |  |  |  |

3.- Trasladar el comportamiento del sistema a una Tabla de verdad

|    | anne | E | ntrad | as | Sal | idas |    |

|----|------|---|-------|----|-----|------|----|

| m  | Α    | В | С     | D  | Е   | Al   | AA |

| 0  | 0    | 0 | 0     | 0  | 0   |      |    |

| 1  | 0    | 0 | 0     | 0  | 1   |      |    |

| 2  | 0    | 0 | 0     | 1  | 0   |      |    |

| 3  | 0    | 0 | 0     | 1  | 1   |      |    |

| 4  | 0    | 0 | 1     | 0  | 0   |      |    |

| 5  | 0    | 0 | 1     | 0  | 1   |      |    |

| 6  | 0    | 0 | 1     | 1  | 0   |      |    |

| 7  | 0    | 0 | 1     | 1  | 1   |      |    |

| 8  | 0    | 1 | 0     | 0  | 0   |      |    |

| 9  | 0    | 1 | 0     | 0  | 1   |      |    |

| 10 | 0    | 1 | 0     | 1  | 0   |      |    |

| 11 | 0    | 1 | 0     | 1  | 1   |      |    |

| 12 | 0    | 1 | 1     | 0  | 0   |      |    |

| 13 | 0    | 1 | 1     | 0  | 1   |      |    |

| 14 | 0    | 1 | 1     | 1  | 0   |      |    |

| 15 | 0    | 1 | 1     | 1  | 1   |      |    |

| 16 | 1    | 0 | 0     | 0  | 0   |      |    |

| 17 | 1    | 0 | 0     | 0  | 1   |      |    |

| 18 | 1    | 0 | 0     | 1  | 0   |      |    |

| 19 | 1    | 0 | 0     | 1  | 1   |      |    |

| 20 | 1    | 0 | 1     | 0  | 0   |      |    |

| 21 | 1    | 0 | 1     | 0  | 1   |      |    |

| 22 | 1    | 0 | 1     | 1  | 0   |      |    |

| 23 | 1    | 0 | 1     | 1  | 1   |      |    |

| 24 | 1    | 1 | 0     | 0  | 0   |      |    |

| 25 | 1    | 1 | 0     | 0  | 1   |      |    |

| 26 | 1    | 1 | 0     | 1  | 0   |      |    |

| 27 | 1    | 1 | 0     | 1  | 1   |      |    |

| 28 | 1    | 1 | 1     | 0  | 0   |      |    |

| 29 | 1    | 1 | 1     | 0  | 1   |      |    |

| 30 | 1    | 1 | 1     | 1  | 0   |      |    |

| 31 | 1    | 1 | 1     | 1  | 1   | _    | _  |

#### Formas canónicas

| Torring ourierings                      |   |                     |     |   |  |  |

|-----------------------------------------|---|---------------------|-----|---|--|--|

|                                         |   | No de Combinaciones |     |   |  |  |

| <b>FAI</b> (A, B, C, D, E) =            | Σ |                     | SOP | 1 |  |  |

| <b>FAA</b> <sub>(A, B, C, D, E)</sub> = | Σ |                     | 301 |   |  |  |

| <b>FAI</b> <sub>(A, B, C, D, E)</sub> = | П |                     | POS | 0 |  |  |

| <b>FAA</b> (A, B, C, D, E) =            | П |                     |     |   |  |  |

# 4.- Ecuaciones Mínimas usando LogicAid

|                                         |  | In | Gates |

|-----------------------------------------|--|----|-------|

| <b>FAI</b> (A, B, C, D, E) =            |  |    |       |

| <b>FAA</b> <sub>(A, B, C, D, E)</sub> = |  |    |       |

| <b>FAI</b> (A, B, C, D, E) =            |  |    |       |

| <b>FAA</b> <sub>(A, B, C, D, E)</sub> = |  |    |       |

| Imagen de la simulación Test_vectors       |  |  |  |  |  |

|--------------------------------------------|--|--|--|--|--|

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

| Distribución de terminales PIN OUT         |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

| Imagen del diagrama esquemático en PROTEUS |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

| Fate del mustatine amusedo                 |  |  |  |  |  |

| Foto del prototipo armado                  |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

|                                            |  |  |  |  |  |

Para la realización de este proyecto formativo se te recomienda consultar los videos siguientes

| DC1 | https://www.youtube.com/watch?v=HgHd7P8XYRs&t=205s |  |

|-----|----------------------------------------------------|--|

| 2   | https://www.youtube.com/watch?v=klSqs3H4ADA&t=17s  |  |

| DC3 | https://www.youtube.com/watch?v=ym4stKMx_5Y&t=6s   |  |

Reporte sesión 6 (lista de Cotejo, Check List)

| 176 | eporte Sesion 6 (lista de Cotejo, Check List)                                                 |

|-----|-----------------------------------------------------------------------------------------------|

| 1   | Portada con datos completos.                                                                  |

| 2   | Redacción del problema propuesto                                                              |

| 3.  | Diagrama de Bloques                                                                           |

| 4   | Tabla de verdad                                                                               |

| 5   | Las ecuaciones SOP y POS en la forma Canónica                                                 |

| 6   | Ecuaciones mínimas indicando el numero de entradas y el numero de compuertas                  |

| 7   | El código ABEL-HDL Truth_Table o Ecuaciones incluyendo el test_vectors en el mismo código.    |

| 8   | Imagen de la simulación (Test Vectors).                                                       |

| 9   | Las ecuaciones mínimas del archivo reporte (RPT).                                             |

| 10  | La distribución de terminales (Pin Out) del archivo reporte (RPT).                            |

| 11  | Imagen de la simulación del Test_vectors                                                      |

| 8   | Imagen del circuito en PROTEUS (usando como entradas y salidas botones, resistencias y Led´s) |

| 9   | Foto del prototipo                                                                            |

| 10  | Conclusiones                                                                                  |

| 11  | Recomendaciones                                                                               |

Subir los archivos entregables a Google classroom, antes de la fecha solicitada

| Archivos entregables en Zip o RAR PDF ABL JED Animación P | TEUS |

|-----------------------------------------------------------|------|

|-----------------------------------------------------------|------|

Una vez cumplido lo anterior es necesario agendar y efectuar la entrevista presencial para presentar el prototipo funcionando correctamente, así como explicar los procedimientos y resultados obtenidos en forma oral y escrita.

"Una mente adaptativa tiene una mejor capacidad de aprendizaje".

Pearl Zhu